?用整個硅片做芯片�����?臺積電說可商業(yè)化�����!

據(jù)Digitiimes報道����,盡管對極其昂貴的��、類似Cerebras Systems開發(fā)的Wafer Scale Engine(WSE)那樣的超級計算機AI芯片的需求仍然很有限����,但臺積電依然計劃在兩年內(nèi)投入類似芯片的商業(yè)生。報道指出�����,能實現(xiàn)這個的關(guān)鍵是臺積電(TSMC)能夠通過其InFO_SoW(集成的扇出晶圓上系統(tǒng))IC縮放工藝來提高其良率���。

Digitimes進一步表示����,Nvidia的GPU Ampere系列和富士通超級計算機Fugaku都已經(jīng)采用了臺積電的晶圓上晶圓上芯片(CoWoS)封裝工藝�����。

要了解臺積電在這里構(gòu)建的內(nèi)容,需要解析多個縮寫�����。集成式扇出是臺積電多年來提供的一種封裝技術(shù)�����。通常���,在將硅片結(jié)合到封裝之前將硅片切成裸片����,那么得到的封裝將大于物理裸片�。

對于那些需要絕對最小裸片尺寸的公司,這種安排并不理想���。為此他們提供了另一種技術(shù)��,稱為晶圓級處理����,通過封裝仍為晶圓一部分的裸片來消除尺寸差異���。這樣可以節(jié)省大量空間�����,但會限制芯片可用的電氣連接數(shù)量��。

InFO通過將更傳統(tǒng)的模切工藝與其他步驟相結(jié)合來解決此限制�,從而保留了晶圓級加工(WLP)產(chǎn)生的大部分尺寸優(yōu)勢�����。以常規(guī)方式切割die��,然后將其重新安裝在第二個晶圓上�����,每個die之間留有額外的空間用于連接�����。3Dincites 根據(jù)臺積電在ECTC 2020上的演講,對InFO_SoW 進行了深入研究�����。InFO_SoW的重點是利用InFO提供的優(yōu)勢并將其擴展到晶圓尺寸的處理模塊���。

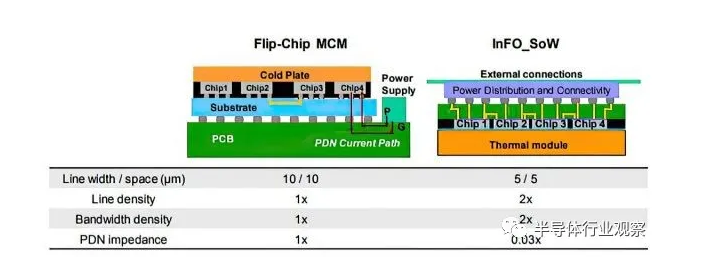

晶圓級處理的理論優(yōu)勢之一是以最小的功耗實現(xiàn)了巨大的連接性���。下面的幻燈片說明了其中的一些差異,包括PDN(配電網(wǎng)絡)阻抗的顯著降低����。這些說法與去年研究小組報告的有關(guān)晶圓級處理的陳述相呼應。研究小組對這一想法進行了調(diào)查�����,認為這是現(xiàn)代時代擴展CPU性能的一種可行方法�。

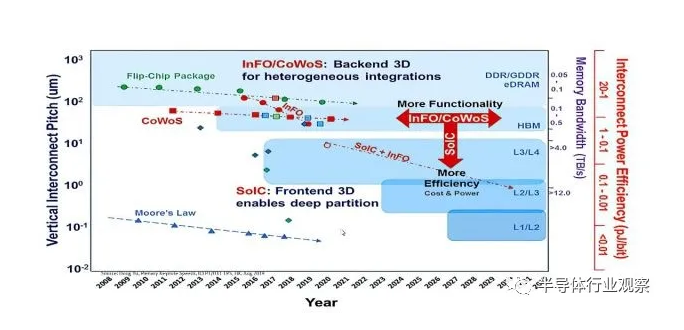

InFO_SoW只是臺積電提供的一種高級封裝技術(shù)。下面的幻燈片顯示了其各種封裝選項在功率效率和垂直互連間距方面的比較�。

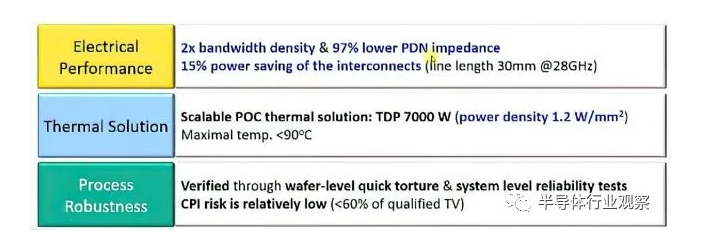

臺積電表示,它可以將帶寬密度提高2倍��,阻抗降低97%�,同時將互連功耗降低15%。

此外,這個芯片的TDP令人驚嘆�。即使我知道這個數(shù)字是針對整個12英寸晶圓的,但7,000W TDP還是讓人大開眼界�。而臺積電正在為Cerebras建造“芯片”,其中包含40萬個內(nèi)核和1.2萬億個晶體管�����。

如果您考慮一下����,AMD和英特爾近年來所擁護的大多數(shù)進步都是互連和封裝方面的改進���。小芯片及其相關(guān)的包裝要求�����,以及HyperTransport Infinity Fabric 的開發(fā)和演變一直是AMD討論的主要話題�。同時�����,英特爾已經(jīng)與EMIB�����,F(xiàn)overos和Omni-Path進行了合作。

如今���,每個人都專注于封裝的原因是因為越來越難以通過縮小die和改進工藝節(jié)點來使晶體管獲得更好的性能���。改善封裝技術(shù)是公司試圖在不違反物理定律的前提下提高性能的方法之一。

這些晶圓級處理器永遠不會成為您在家中安裝的設備�。Cerebras晶圓的估計成本為200萬美元。晶圓級處理使我感興趣的是�����,無論功能多么強大���,云最終都可以在任何單個桌面安裝上建立真正的優(yōu)勢�。從理論上講�����,只要我們能夠解決延遲問題�,晶圓級處理+云計算就可以改變計算領(lǐng)域。

世界最大芯片Wafer Scale Engine(WSE)的誕生

去年八月����,初創(chuàng)公司Cerebras Systems宣布推出有史以來最大的芯片Wafer Scale Engine(WSE)��。

據(jù)悉����,WSE擁有1.2萬億個晶體管�,這是一個什么概念呢?比較一下�,1971年英特爾首款4004處理器擁有2300個晶體管��,最近����,AMD推出的最新處理器擁有320億個晶體管。由此可見WSE規(guī)模之龐大��。

大多數(shù)芯片是在12英寸硅晶圓上制造的����,并在芯片工廠中批量處理。但Cerebras Systems芯片是在單個晶圓上通過互聯(lián)實現(xiàn)的單芯片���。這些互連設計使其全部保持高速運行��,可使萬億個晶體管全部一起工作��。

Cerebras Wafer Scale Engine專門針對處理人工智能應用程序而設計的�����。該公司本周正在加利福尼亞州帕洛阿爾托的斯坦福大學舉行的Hot Chips會議上討論這項設計����。

此前,三星已經(jīng)制造了一個閃存芯片�����,即eUFS���,擁有2萬億個晶體管����。但Cerebras芯片擁有400,000個核心��,42,225平方毫米�����。它比最大的Nvidia圖形處理單元大 56.7倍,該單元的尺寸為815平方毫米和211億個晶體管�。

與傳統(tǒng)芯片相比,WSE還包含3000倍的高速片上存儲器����,并且具有10000倍的存儲器帶寬。

該芯片來自Andrew Feldman領(lǐng)導的團隊���,后者曾創(chuàng)建微型服務器公司SeaMicro����,并以3.34億美元的價格出售給了AMD����。

芯片尺寸在AI中非常重要����,因為大芯片可以更快地處理信息,在更短的時間內(nèi)產(chǎn)生答案��。減少訓練時間��,使研究人員能夠測試更多想法���,使用更多數(shù)據(jù)并解決新問題�����。谷歌�����,F(xiàn)acebook����,OpenAI,騰訊���,百度和許多專業(yè)人士都認為��,今天人工智能的主要限制是訓練需要很長時間����。因此�����,縮短訓練時間就消除了整個行業(yè)進步的主要瓶頸�����。

當然,芯片制造商通常不會制造如此大的芯片�����。在單個晶圓上�����,在制造過程中通常會產(chǎn)生一些雜質(zhì)�,雜質(zhì)會導致芯片發(fā)生故障。如果晶圓上只有一個芯片�,它有雜質(zhì)的幾率是100%,雜質(zhì)會使芯片失效����。但Cerebras設計的芯片是有冗余的�,因此一種雜質(zhì)不會破壞整個芯片。

WSE有很多創(chuàng)新��,通過解決限制芯片尺寸的數(shù)十年的技術(shù)挑戰(zhàn) - 例如交叉光罩連接����,良率�,功率輸送���,以及封裝等�,Cerebras Systems首席執(zhí)行官費爾德曼說��。“每個架構(gòu)決策都是為了優(yōu)化AI工作的性能�。結(jié)果是,Cerebras WSE根據(jù)工作量提供了數(shù)百或數(shù)千倍于現(xiàn)有解決方案的性能�����,只需很小的功耗和空間���。“

WSE通過加速神經(jīng)網(wǎng)絡訓練的所有元素來實現(xiàn)這些性能提升���。神經(jīng)網(wǎng)絡是多級計算反饋回路。較快的輸入在循環(huán)中移動��,循環(huán)學習的速度越快�����,從而減少了訓練時間。

Linley Group首席分析師Linley Gwennap在一份聲明中說:“Cerebras憑借其晶圓級技術(shù)實現(xiàn)了巨大的飛躍�,在單片晶圓上實現(xiàn)了更多的處理性能。” 為了實現(xiàn)這一壯舉�,該公司已經(jīng)解決了一系列工程難題,包括實施高速芯片到芯片通信�����,解決制造缺陷��,封裝如此大的芯片���,以及電源和冷卻等問題�。通過將各種學科的頂級工程師聚集在一起�����,Cerebras在短短幾年內(nèi)創(chuàng)造了新技術(shù)并交付了產(chǎn)品�����。

據(jù)悉���,該芯片面積比最大的GPU多56.7倍,Cerebras WSE提供更多內(nèi)核進行計算,更多內(nèi)存靠近內(nèi)核���,因此內(nèi)核可以高效運行��。由于這些大量的內(nèi)核和內(nèi)存位于單個芯片上�����,因此所有通信都在芯片內(nèi)進行�����,這意味著它的低延遲通信帶寬是巨大的����,因此內(nèi)核組可以以最高效率進行協(xié)作����。

Cerebras WSE中的46,225平方毫米的硅包含400,000個AI優(yōu)化,無緩存���,無開銷的計算內(nèi)核和18千兆字節(jié)的本地�����、分布式���、超高速SRAM內(nèi)存��,內(nèi)存帶寬為每秒9 PB�。這些內(nèi)核通過細粒度�、全硬件、片上網(wǎng)狀連接通信網(wǎng)絡連接在一起�����,可提供每秒100 petabits的總帶寬����。更多內(nèi)核,更多本地內(nèi)存和低延遲高帶寬結(jié)構(gòu)共同構(gòu)成了加速AI工作的最佳架構(gòu)���。

WSE包含400,000個AI優(yōu)化的計算核心���。被稱為稀疏線性代數(shù)核心的SLAC,計算核心靈活�、可編程,并針對支持所有神經(jīng)網(wǎng)絡計算的稀疏線性代數(shù)進行了優(yōu)化�。SLAC的可編程性確保內(nèi)核可以在不斷變化的機器學習領(lǐng)域中運行所有神經(jīng)網(wǎng)絡算法����。

由于稀疏線性代數(shù)核心針對神經(jīng)網(wǎng)絡計算基元進行了優(yōu)化�,因此它們可實現(xiàn)最佳利用率 - 通常是GPU的三倍或四倍�����。此外���,WSE核心包括Cerebras發(fā)明的稀疏性收集技術(shù)�,以加速稀疏工作負載(包含零的工作負載)的計算性能����,如深度學習。

零在深度學習計算中很普遍��。通常�����,要相乘的向量和矩陣中的大多數(shù)元素都是零��。然而���,乘以零是浪費硅����、功率和時間,因為沒有新的信息��。

因為GPU和張量處理單元是密集的執(zhí)行引擎 - 設計為永不遇到零的引擎 - 它們即使在零時也會乘以每個元素�����。當50%-98%的數(shù)據(jù)為零時�����,如深度學習中的情況一樣��,大多數(shù)乘法都被浪費了�����。由于Cerebras稀疏線性代數(shù)核不會乘以零�����,所有零數(shù)據(jù)都會被濾除��,并且可以在硬件中跳過。

內(nèi)存是每個計算機體系結(jié)構(gòu)的關(guān)鍵組件��。更接近計算的內(nèi)存轉(zhuǎn)換為更快的計算���,更低的延遲和更好的數(shù)據(jù)移動功效�����。高性能深度學習需要大量計算,并且頻繁訪問數(shù)據(jù)���。這需要計算核心和存儲器之間的緊密接近���,這在GPU中并非如此,其中絕大多數(shù)存儲器是很緩慢的�,且在片外。

Cerebras Wafer Scale Engine包含更多內(nèi)核����,具有比迄今為止任何芯片更多的本地內(nèi)存,并且在一個時鐘周期內(nèi)可以通過其核心訪問18GB的片上內(nèi)存�����。WSE上的核心本地內(nèi)存集合可提供每秒9PB的內(nèi)存帶寬 - 比領(lǐng)先的圖形處理單元多3,000倍的片上內(nèi)存和10,000倍的內(nèi)存帶寬。

Swarm通信結(jié)構(gòu)是WSE上使用的處理器間通信結(jié)構(gòu)��,它可以傳統(tǒng)通信技術(shù)的功耗的一小部分實現(xiàn)突破性帶寬和低延遲��。Swarm提供低延遲��、高帶寬的2D網(wǎng)格���,可連接WSE上的所有400,000個核心���,每秒帶寬為100 petabits。

路由方面��,Swarm為每個神經(jīng)網(wǎng)絡提供獨特的優(yōu)化通信路徑����。軟件根據(jù)正在運行的特定用戶定義的神經(jīng)網(wǎng)絡結(jié)構(gòu),配置通過400,000個核心的最佳通信路徑以連接處理器�。

Cerebras WSE的總帶寬為每秒100 petabits。不需要諸如TCP / IP和MPI之類的通信協(xié)議支持�����,因此避免了它們的性能損失����。該架構(gòu)中的通信能量成本遠低于每比特1焦耳�����,這比GPU低近兩個數(shù)量級����。通過結(jié)合大量帶寬和極低的延遲�����,Swarm通信結(jié)構(gòu)使Cerebras WSE能夠比任何當前可用的解決方案更快地學習���。(轉(zhuǎn)自半導體行業(yè)觀察)